Chapter 1 使用目的

i.MX8 / MSCALE DDR Tool 是一個(gè) PC 端運(yùn)行的軟件應(yīng)用程序,可以將測(cè)試映像檔,透過 USB 連接到 i.MX 系列處理器,做 DDR Training 、Code Generation (產(chǎn)生參數(shù)程式碼)、Stress Test (壓力測(cè)試),目的是幫助驗(yàn)證 DDR 穩(wěn)定性。

Chapter 2 檔案下載

2.1 RPA 和 DDR Stress Test 下載

載下網(wǎng)址: https://community.nxp.com/docs/DOC-340179

下載下列檔案:

1. DDR_stress_test_subtest_description.pdf

2. mscale_ddr_tool_v300_setup.zip

3. MX8M_DDR3L_RPA_v6.xlsx

4. MX8M_DDR4_RPA_v9.xlsx

5. MX8M_LPDDR4_RPA_v24.xlsx

6. MX8M_Mini_DDR3L_RPA_v7.xlsx

7. MX8M_Mini_DDR4_RPA_v10.xlsx

8. MX8M_Mini_LPDDR4_RPA_v15.xlsx

9. MX8M_Nano_DDR4_RPA_v2.xlsx

10. preliminary_MX8M_Nano_DDR3L_RPA_v1.xlsx

11. preliminary_MX8M_Nano_LPDDR4_RPA_v1.xlsx

Chapter 3 RPA 檔案

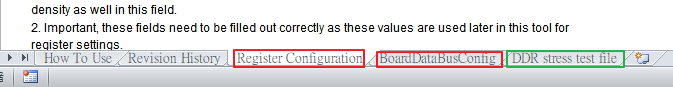

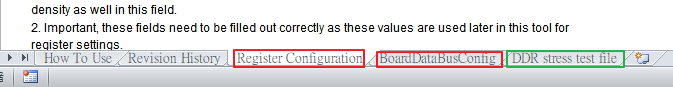

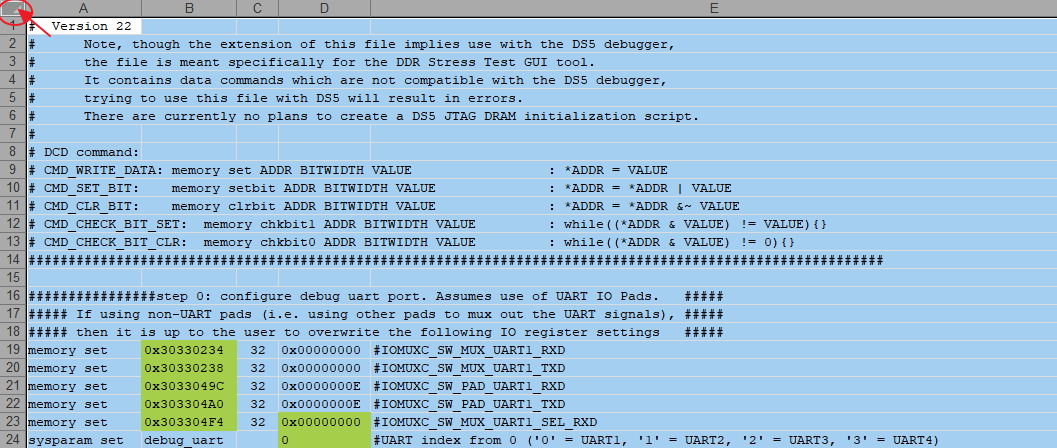

MX8M_LPDDR4_RPA_v22.xlsx 就是 RPA (Register Programming Aid) 檔案,用來(lái)是產(chǎn)生 NXP iMX/Mscale DDR Tool 使用的設(shè)定檔 (副檔名 .ds) Script,RPA 檔案是Excel 檔案格式,依據(jù) "Register Configuration" Worksheet 和 " BoardDataBusConfig" Worksheet 內(nèi)部表格參數(shù)設(shè)定,產(chǎn)生 " DDR stress test file" Worksheet。

3.1 Register Configuration

3.1.1 LPDDR4 資訊

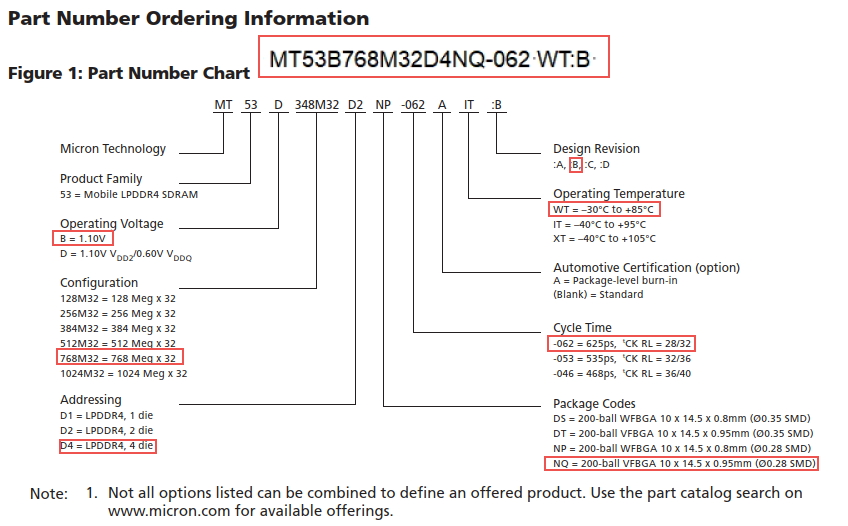

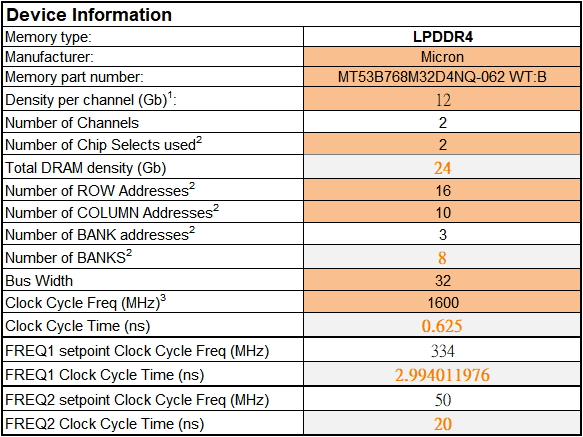

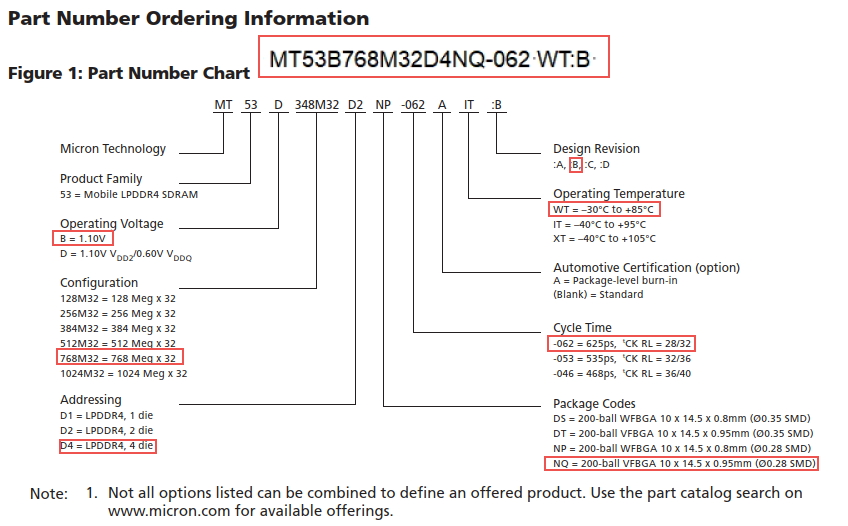

MCIMX8M-EVK使用 LPDDR4 料號(hào) MT53B768M32D4NQ-062 WT:B ,由 Datasheet 提供 Part Name Ordering Information 如下。

3.1.2 填寫要點(diǎn)

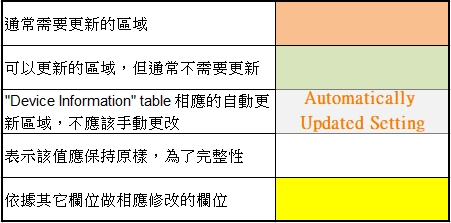

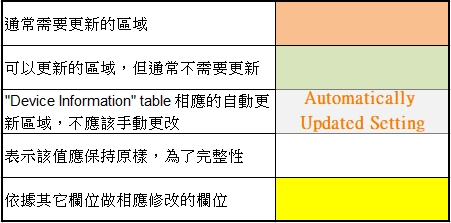

不同顏色的欄位的意義如下,很多情況下,欄位是不需要更新的。

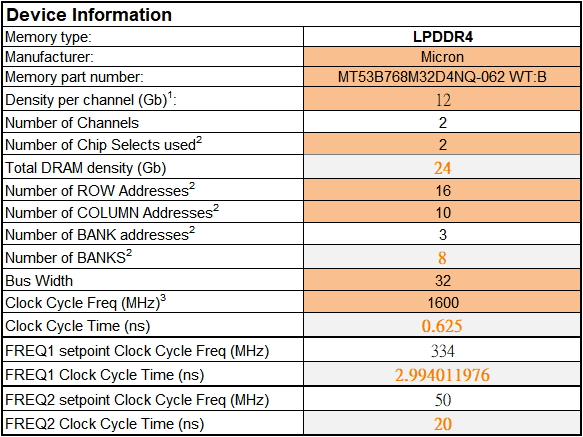

3.1.3 填寫結(jié)果

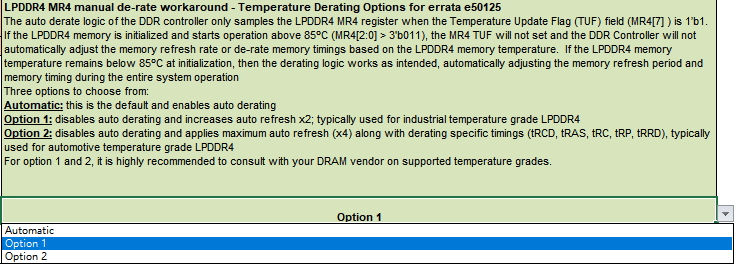

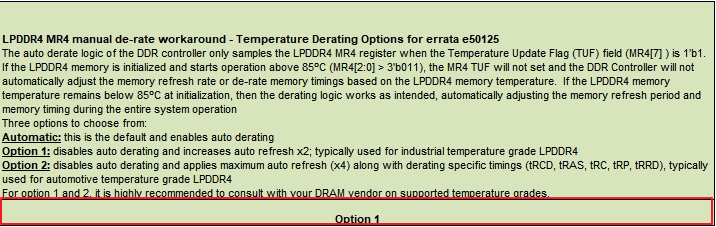

此次本版更新中特別提醒大家,請(qǐng)確認(rèn)使用晶片的溫度規(guī)範(fàn),此參數(shù)會(huì)影響系統(tǒng)的穩(wěn)定度。

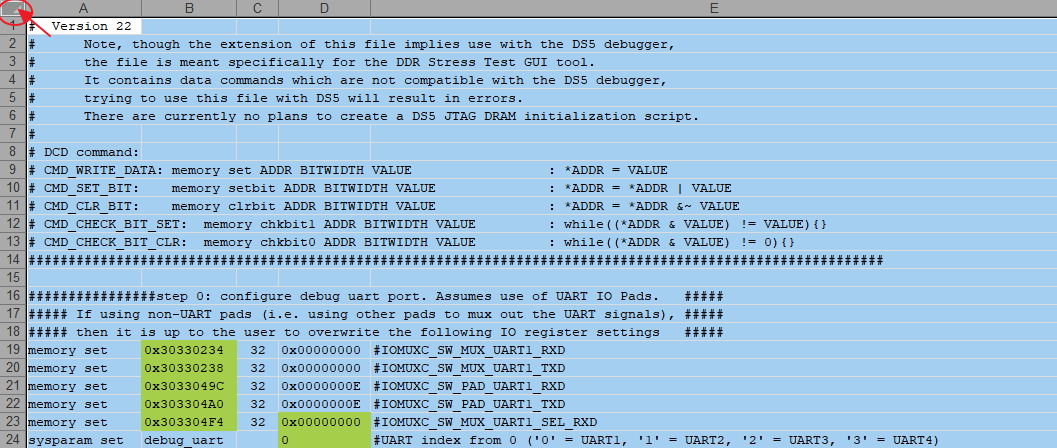

3.2 DDR Stress Test file

點(diǎn)選下圖紅框箭頭,複製此工作表全部?jī)?nèi)容貼到純文字檔中,並使用“.ds”副檔名命名該文字檔,執(zhí)行DDR壓力測(cè)試時(shí)需要使用此檔 (mx8m_micron_lpddr4.ds)。

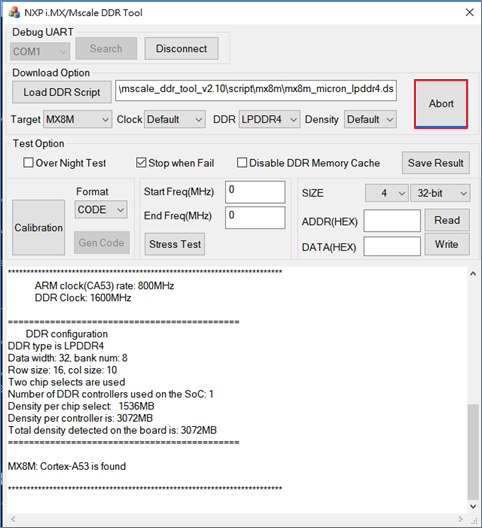

Chapter 4 i.MX8/MSCALE DDR TOOL

i.MX8/MSCALE DDR TOOL 就是 NXP i.MX8 系列的 DDR Stress Test Tool,透過 USB 下載測(cè)試 Image 到 i.MX 系列處理器,做相關(guān) RAM參數(shù)調(diào)校,由於運(yùn)行在 PC 端時(shí)會(huì)存取 Windows Registry,所以必須用 Administrator 權(quán)限執(zhí)行。

4.1 硬體設(shè)定 --- MCIMX8M-EVK

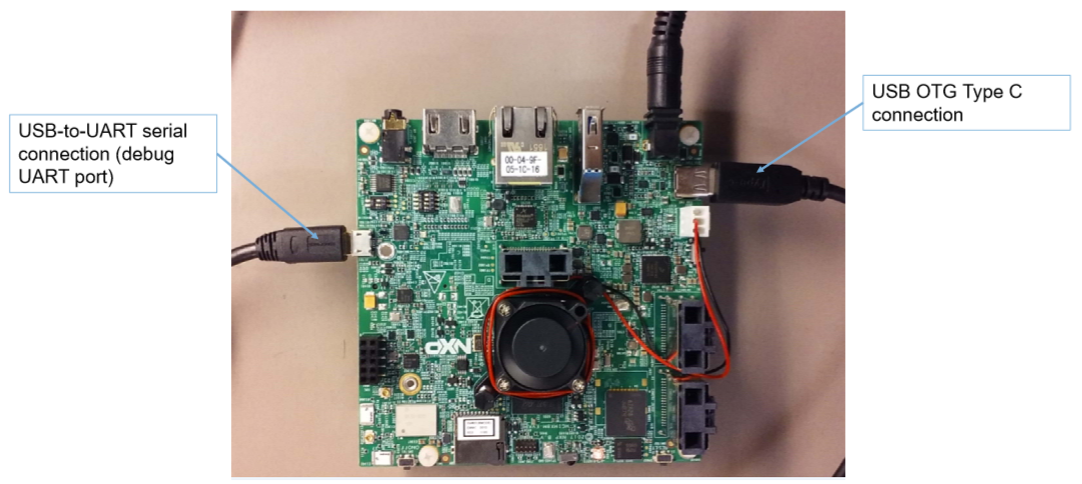

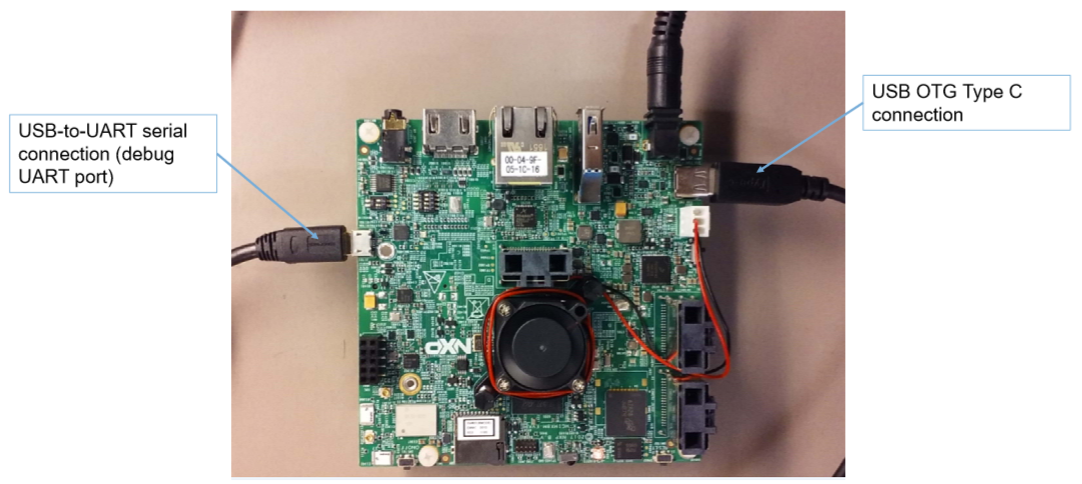

1. MCIMX8M-EVK 連接方法請(qǐng)參考下圖。

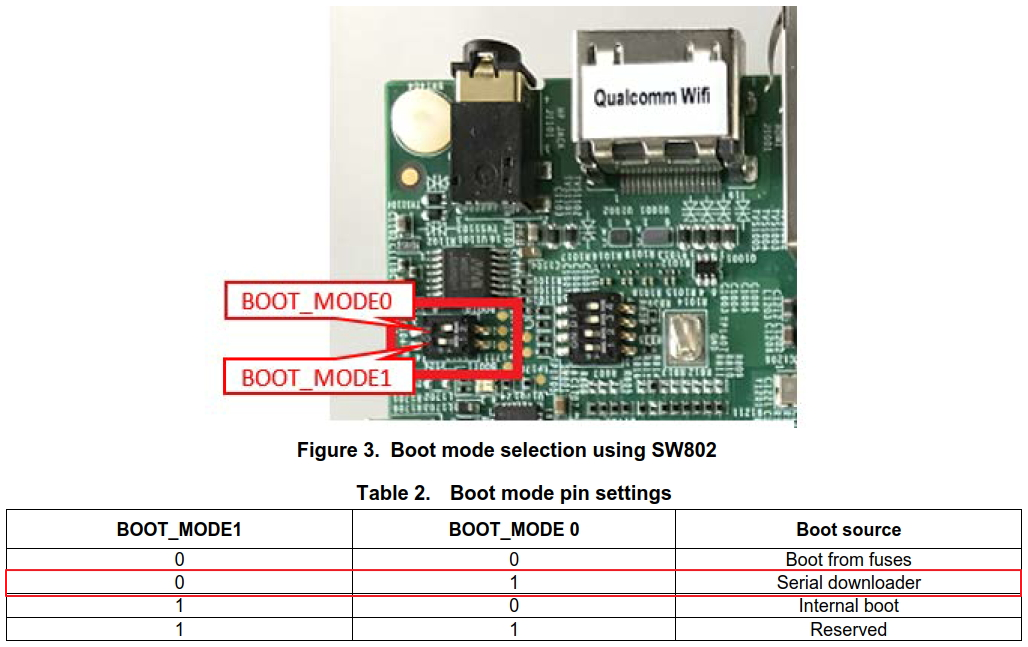

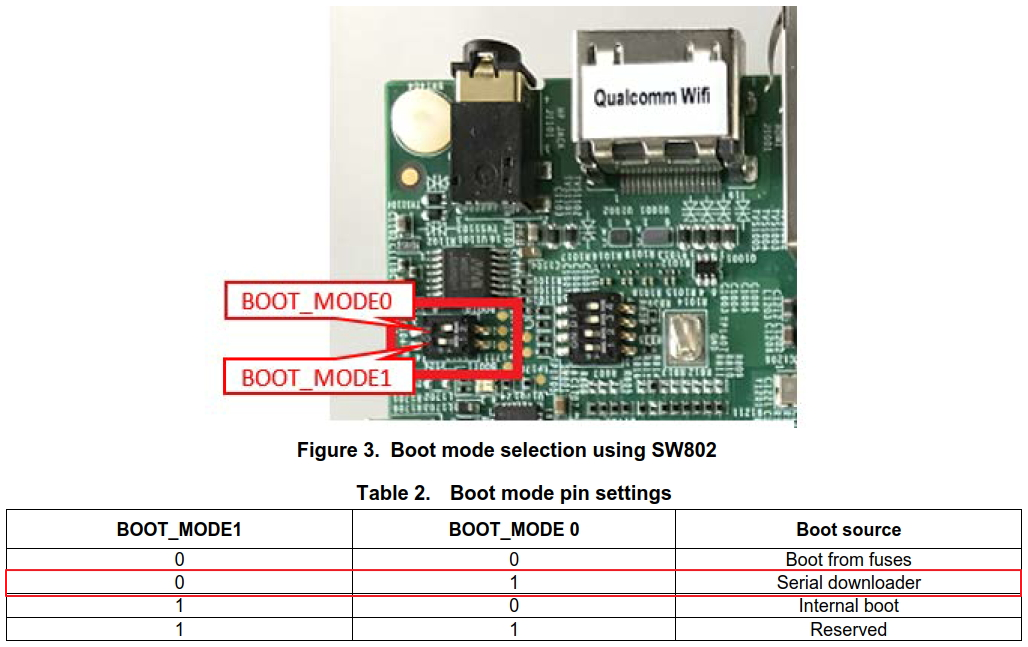

2. Bootmode 設(shè)定為 Uart Mode (Serial Downloader),請(qǐng)參考下圖。

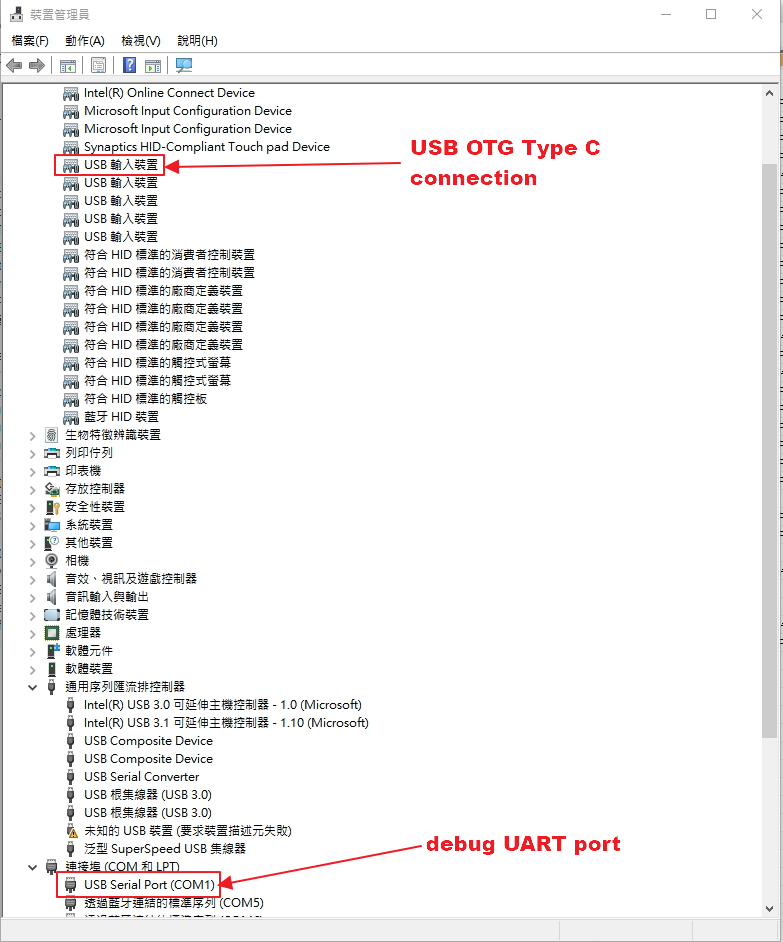

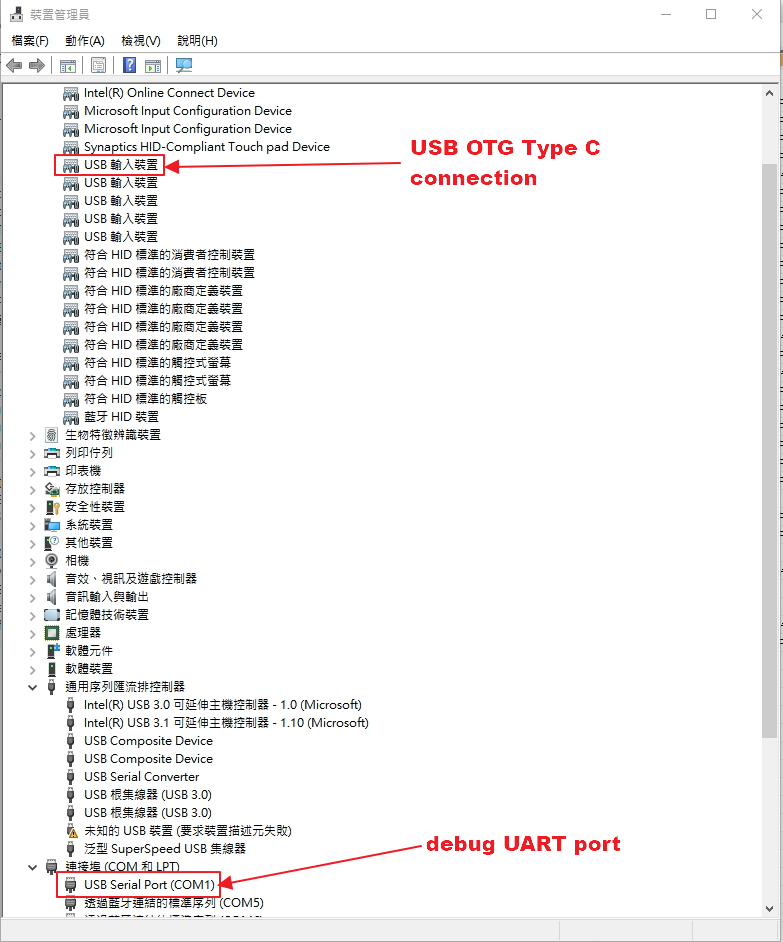

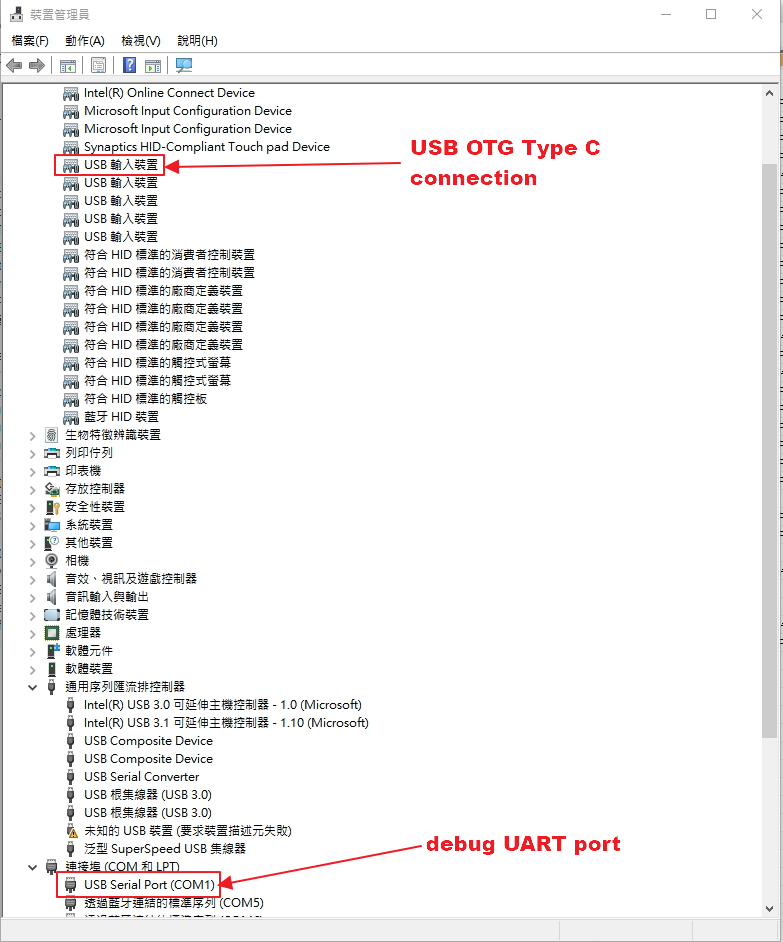

3. 開啟電源後,確認(rèn)裝置管理員可以辨識(shí)到裝置,請(qǐng)參考下圖。

4.2 硬體設(shè)定 --- OP-Doflamingo EVM

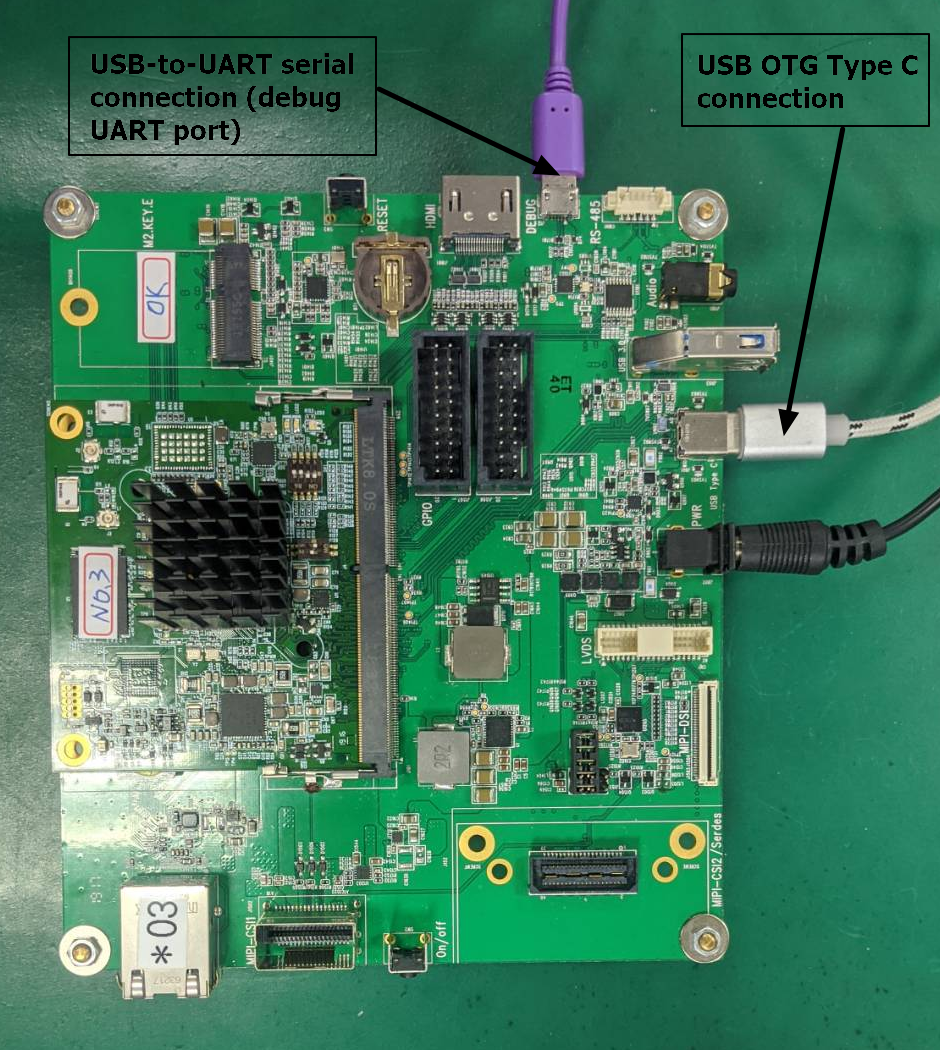

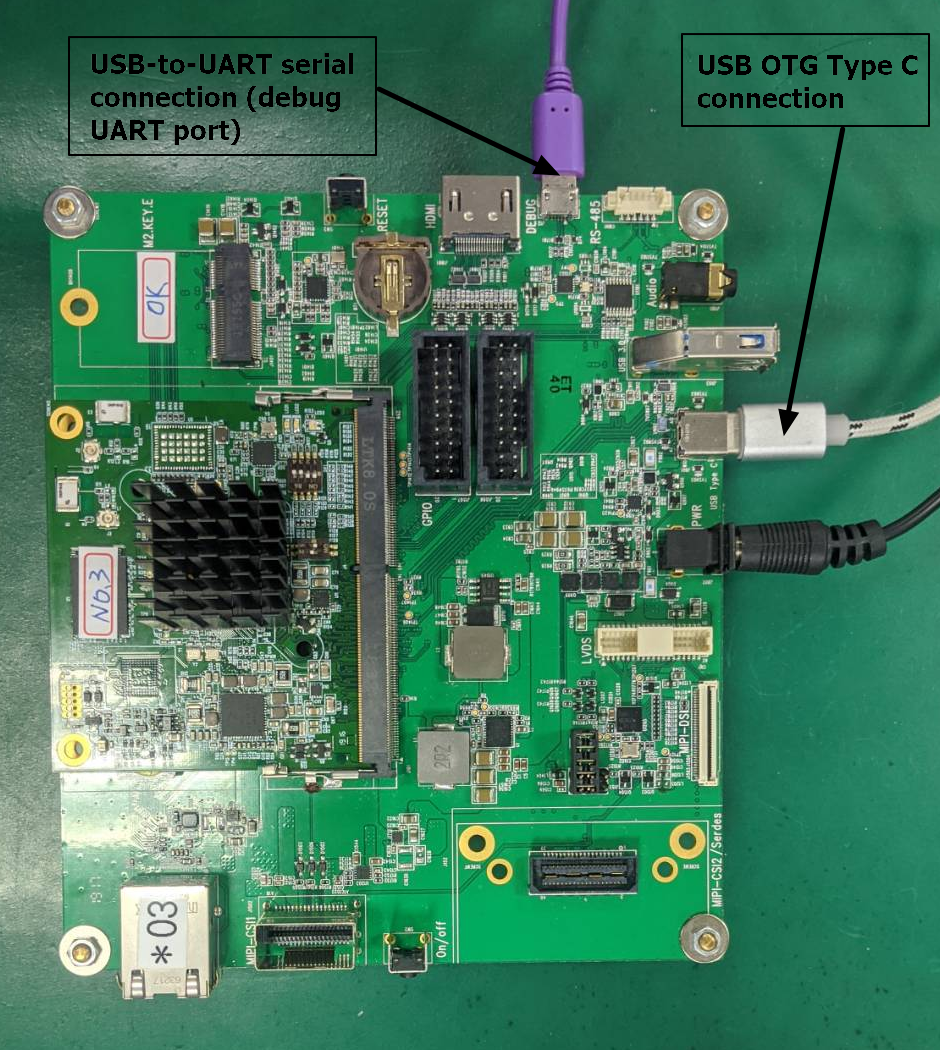

1. OP-Doflamingo EVM 連接方法請(qǐng)參考下圖。

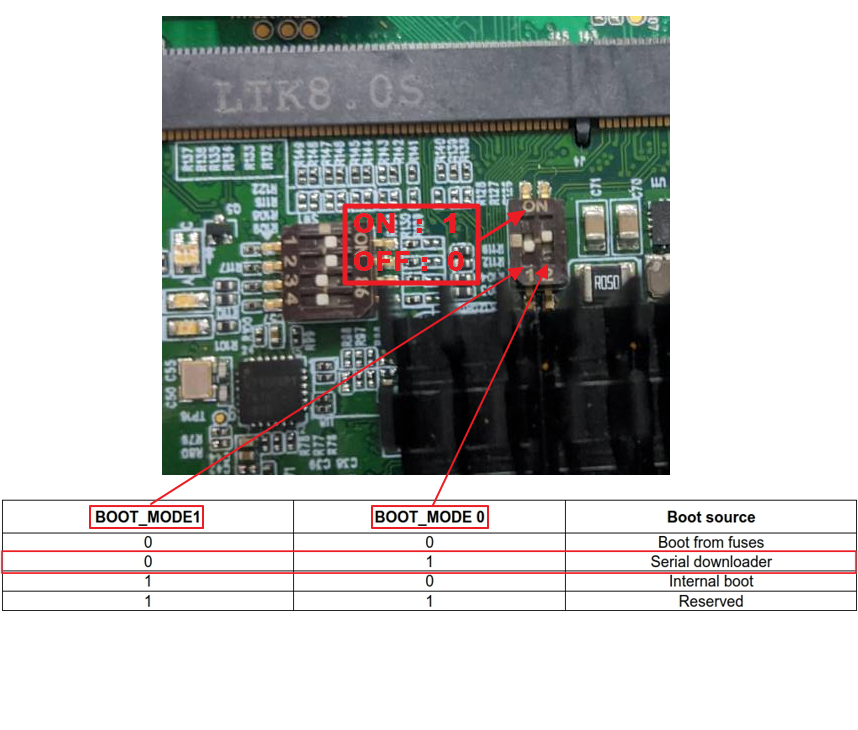

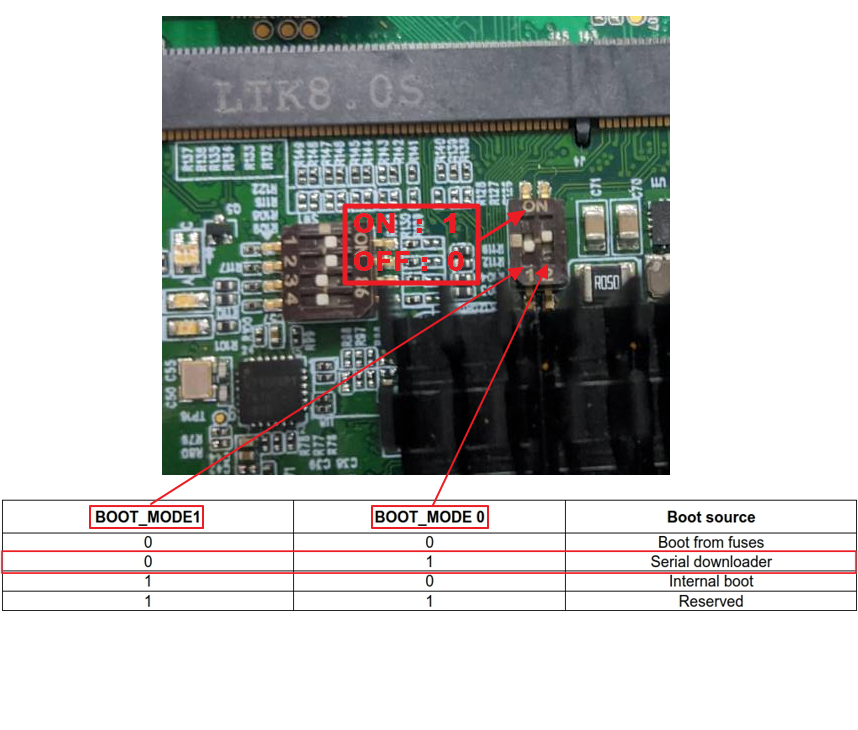

2. Bootmode 設(shè)定為 Uart Mode (Serial Downloader),請(qǐng)參考下圖。

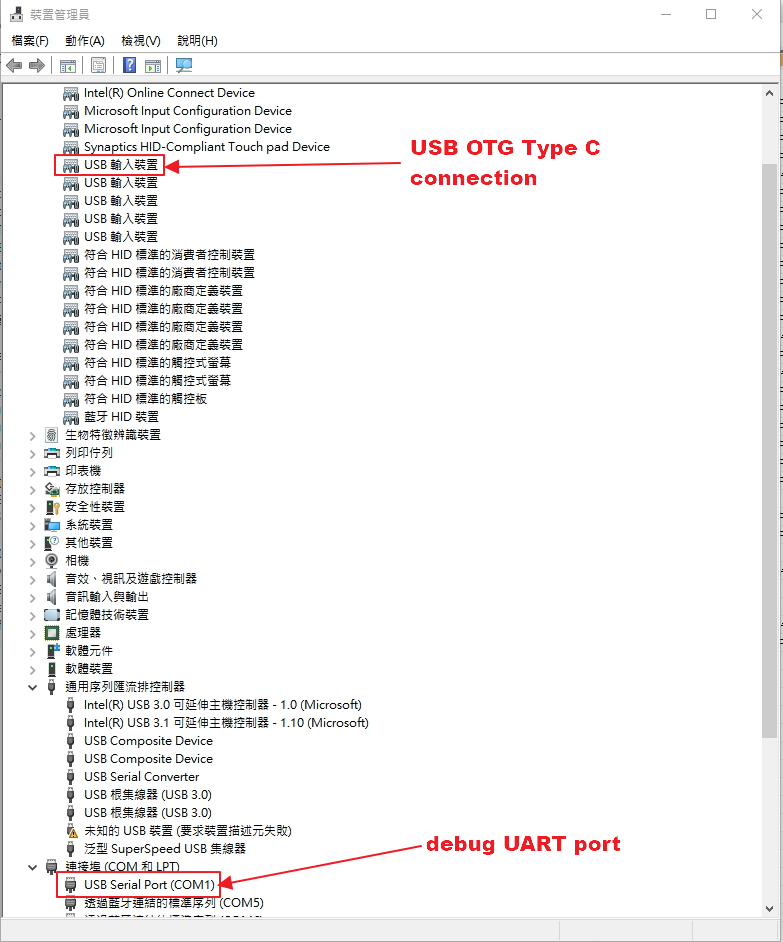

3. 開啟電源後,確認(rèn)裝置管理員可以辨識(shí)到裝置,請(qǐng)參考下圖。

4.3 軟體安裝

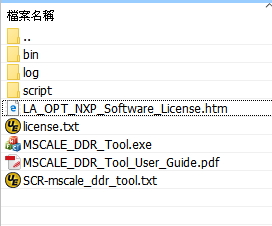

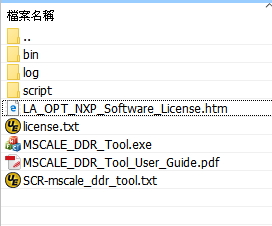

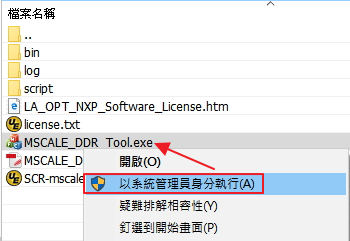

解壓縮 mscale_ddr_tool_v300_setup.zip 並執(zhí)行 mscale_ddr_tool_v300_setup.exe 安裝檔後,得到 “mscale_ddr_tool” 資料夾,資料夾內(nèi)容說(shuō)明如下:

* MSCALE_DDR_Tool.exe : PC 端軟體

* MSCALE_DDR_Tool_User_Guide.docx : 使用說(shuō)明檔

* SCR-mscale_ddr_tool.txt : 版權(quán)資訊

* bin : MX8MSCALE 內(nèi)部執(zhí)行Binaries 檔案

* log : 測(cè)??記錄檔

* script : Script 初始設(shè)定檔案

4.4 軟體執(zhí)行

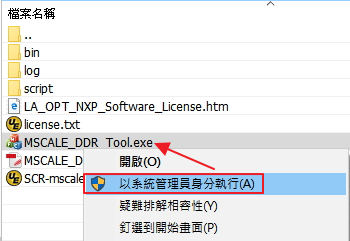

在 “mscale_ddr_tool” 資料夾內(nèi),使用 Administrator 權(quán)限 (系統(tǒng)管理員身分) 執(zhí)行 MSCALE_DDR_Tool.exe。

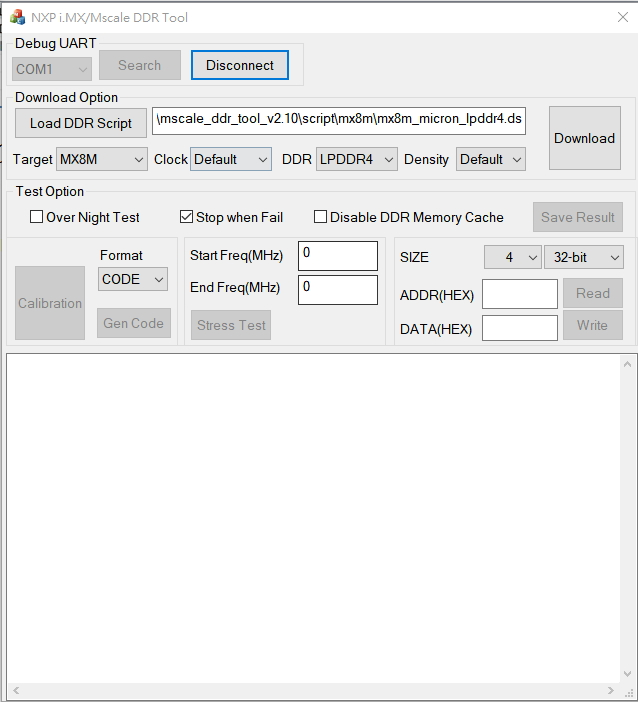

4.4.1 介面說(shuō)明

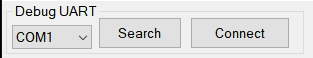

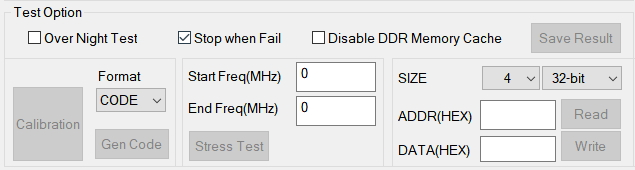

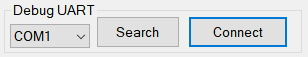

1. Debug UART 區(qū)域

UART 下拉選單:UART Port選擇

Search Button:搜尋電腦 UART Port 列表,並顯示在 UART Port下拉選單

Connect Button:連結(jié) UART Port 下拉選單,選擇的 UART Port

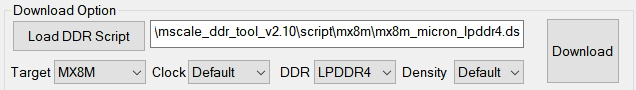

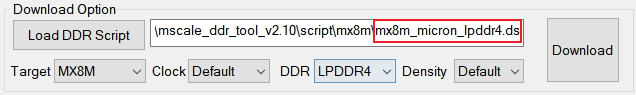

2. Download Option 區(qū)域

Load DDR Script:選擇 DDR Initialization Script 檔案

TARGET 下拉選單:選擇測(cè)試的目標(biāo)板子

i.MX8 / MSCALE DDR Tool 是一個(gè) PC 端運(yùn)行的軟件應(yīng)用程序,可以將測(cè)試映像檔,透過 USB 連接到 i.MX 系列處理器,做 DDR Training 、Code Generation (產(chǎn)生參數(shù)程式碼)、Stress Test (壓力測(cè)試),目的是幫助驗(yàn)證 DDR 穩(wěn)定性。

Chapter 2 檔案下載

2.1 RPA 和 DDR Stress Test 下載

載下網(wǎng)址: https://community.nxp.com/docs/DOC-340179

下載下列檔案:

1. DDR_stress_test_subtest_description.pdf

2. mscale_ddr_tool_v300_setup.zip

3. MX8M_DDR3L_RPA_v6.xlsx

4. MX8M_DDR4_RPA_v9.xlsx

5. MX8M_LPDDR4_RPA_v24.xlsx

6. MX8M_Mini_DDR3L_RPA_v7.xlsx

7. MX8M_Mini_DDR4_RPA_v10.xlsx

8. MX8M_Mini_LPDDR4_RPA_v15.xlsx

9. MX8M_Nano_DDR4_RPA_v2.xlsx

10. preliminary_MX8M_Nano_DDR3L_RPA_v1.xlsx

11. preliminary_MX8M_Nano_LPDDR4_RPA_v1.xlsx

Chapter 3 RPA 檔案

MX8M_LPDDR4_RPA_v22.xlsx 就是 RPA (Register Programming Aid) 檔案,用來(lái)是產(chǎn)生 NXP iMX/Mscale DDR Tool 使用的設(shè)定檔 (副檔名 .ds) Script,RPA 檔案是Excel 檔案格式,依據(jù) "Register Configuration" Worksheet 和 " BoardDataBusConfig" Worksheet 內(nèi)部表格參數(shù)設(shè)定,產(chǎn)生 " DDR stress test file" Worksheet。

3.1 Register Configuration

3.1.1 LPDDR4 資訊

MCIMX8M-EVK使用 LPDDR4 料號(hào) MT53B768M32D4NQ-062 WT:B ,由 Datasheet 提供 Part Name Ordering Information 如下。

3.1.2 填寫要點(diǎn)

不同顏色的欄位的意義如下,很多情況下,欄位是不需要更新的。

3.1.3 填寫結(jié)果

此次本版更新中特別提醒大家,請(qǐng)確認(rèn)使用晶片的溫度規(guī)範(fàn),此參數(shù)會(huì)影響系統(tǒng)的穩(wěn)定度。

3.2 DDR Stress Test file

點(diǎn)選下圖紅框箭頭,複製此工作表全部?jī)?nèi)容貼到純文字檔中,並使用“.ds”副檔名命名該文字檔,執(zhí)行DDR壓力測(cè)試時(shí)需要使用此檔 (mx8m_micron_lpddr4.ds)。

Chapter 4 i.MX8/MSCALE DDR TOOL

i.MX8/MSCALE DDR TOOL 就是 NXP i.MX8 系列的 DDR Stress Test Tool,透過 USB 下載測(cè)試 Image 到 i.MX 系列處理器,做相關(guān) RAM參數(shù)調(diào)校,由於運(yùn)行在 PC 端時(shí)會(huì)存取 Windows Registry,所以必須用 Administrator 權(quán)限執(zhí)行。

4.1 硬體設(shè)定 --- MCIMX8M-EVK

1. MCIMX8M-EVK 連接方法請(qǐng)參考下圖。

2. Bootmode 設(shè)定為 Uart Mode (Serial Downloader),請(qǐng)參考下圖。

3. 開啟電源後,確認(rèn)裝置管理員可以辨識(shí)到裝置,請(qǐng)參考下圖。

4.2 硬體設(shè)定 --- OP-Doflamingo EVM

1. OP-Doflamingo EVM 連接方法請(qǐng)參考下圖。

2. Bootmode 設(shè)定為 Uart Mode (Serial Downloader),請(qǐng)參考下圖。

3. 開啟電源後,確認(rèn)裝置管理員可以辨識(shí)到裝置,請(qǐng)參考下圖。

4.3 軟體安裝

解壓縮 mscale_ddr_tool_v300_setup.zip 並執(zhí)行 mscale_ddr_tool_v300_setup.exe 安裝檔後,得到 “mscale_ddr_tool” 資料夾,資料夾內(nèi)容說(shuō)明如下:

* MSCALE_DDR_Tool.exe : PC 端軟體

* MSCALE_DDR_Tool_User_Guide.docx : 使用說(shuō)明檔

* SCR-mscale_ddr_tool.txt : 版權(quán)資訊

* bin : MX8MSCALE 內(nèi)部執(zhí)行Binaries 檔案

* log : 測(cè)??記錄檔

* script : Script 初始設(shè)定檔案

4.4 軟體執(zhí)行

在 “mscale_ddr_tool” 資料夾內(nèi),使用 Administrator 權(quán)限 (系統(tǒng)管理員身分) 執(zhí)行 MSCALE_DDR_Tool.exe。

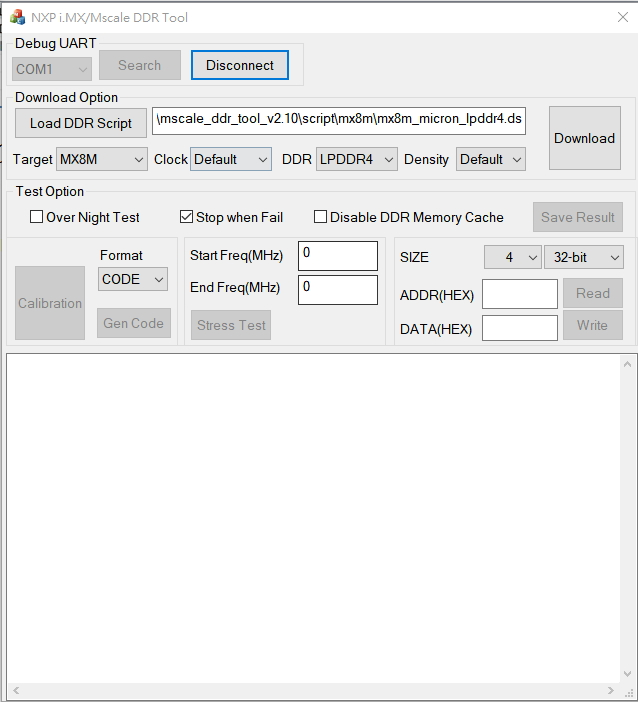

4.4.1 介面說(shuō)明

1. Debug UART 區(qū)域

UART 下拉選單:UART Port選擇

Search Button:搜尋電腦 UART Port 列表,並顯示在 UART Port下拉選單

Connect Button:連結(jié) UART Port 下拉選單,選擇的 UART Port

2. Download Option 區(qū)域

Load DDR Script:選擇 DDR Initialization Script 檔案

TARGET 下拉選單:選擇測(cè)試的目標(biāo)板子

Clock 下拉選單:選擇 ARM CPU Clock,"Default" 意思是使用初始 ARM Clock

DDR 下拉選單:選擇 DDR 型態(tài),有LPDDR4 / DDR4 / DDR3L 三種型態(tài)

Density 下拉選單:選擇 DDR 測(cè)試容量,"Default" 意思是測(cè)試所有容量

Download:依據(jù)選擇的條件,下載 Image 至目標(biāo)平臺(tái)

3. Test Option 區(qū)域

Over Night Test:預(yù)設(shè)壓力測(cè)試做一次停止,此選項(xiàng)被勾選後會(huì)不停的一直做壓力測(cè)試

Stop when Fail:此選項(xiàng)被勾選後,遇到壓力測(cè)試有錯(cuò)誤時(shí)就即刻停止,預(yù)設(shè)會(huì)一直做下去

Disable DDR Memory Cache:此選項(xiàng)決定是否使用 DDR的快取 / 緩衝功能

Format 下拉選單:ARRAY 或 CODE 選項(xiàng),取決於 uboot 版本,BSP L4.14.78_1.0.0_ga ~ L4.19.35_1.1.0_ga 的 uboot版本請(qǐng)使用 ARRAY 選項(xiàng),BSP L4.9.51_imx8m_ga 的 uboot 版本請(qǐng)使用 CODE 選項(xiàng),CODE 選項(xiàng)是為了相容於早期舊的 uboot 版本。

Calibration and Gen Code:必須先執(zhí)行 Calibration按扭,完成校準(zhǔn)工作,才能執(zhí)行 Gen Code 按扭,然後依據(jù) Format 下拉選單產(chǎn)生 DDR initialization Code。

Start / End Freq:可以設(shè)置測(cè)試的頻率範(fàn)圍。保留預(yù)設(shè)為 0 值,它將以 Script 內(nèi)的初始頻率設(shè)定做測(cè)試。如果選擇一個(gè)範(fàn)圍來(lái)測(cè)試,開始頻率必須要設(shè)定在 Script 內(nèi)的初始頻率 ±50MHz 範(fàn)圍內(nèi),結(jié)束頻率必須大於開始頻率且在 100Mhz 以內(nèi)

Stress Test:執(zhí)行壓力測(cè)試

ADDR / DATA (HEX):讀寫 Memory 時(shí),設(shè)定位址和資料的欄位,並可以選擇 8bit / 16bit / 32bit / 64bit 模式

Read / Write:執(zhí)行讀寫 Memory 功能

Save Result:儲(chǔ)存過程和結(jié)果為 Log 檔案。

4.4.2 步驟

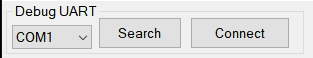

1. 按下 Search 按扭在 Debug UART 區(qū)域,然後選擇正確的 UART Port (Debug UART Port) 連接到 MX8 Cortex A-Core Debug UART , 最後按下 Connect 按扭,請(qǐng)參考下圖。

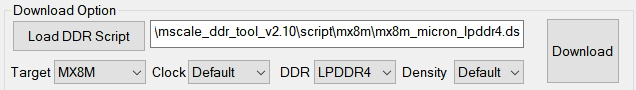

2. 按下 Load DDR Script 按扭選擇在 2.2 DDR Stress Test File 章節(jié)產(chǎn)生的 Script 檔案 (mx8m_micron_lpddr4.ds),並在 Download Option 區(qū)域選擇正確選項(xiàng),請(qǐng)參考下圖。

3. 按下 Download 按扭後,請(qǐng)參考下圖。

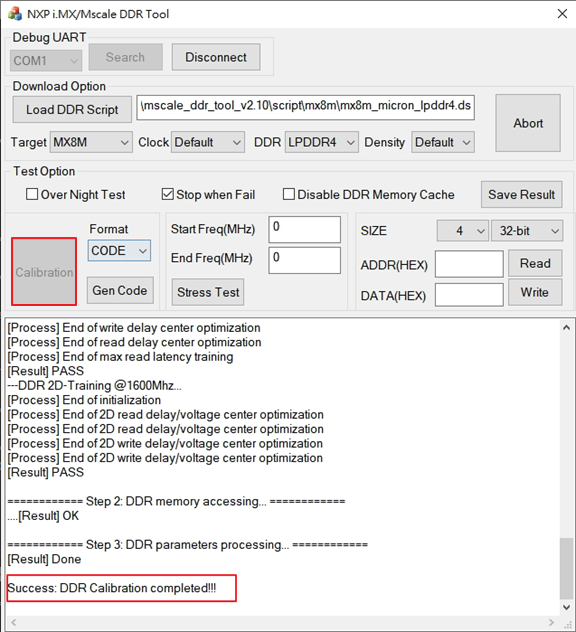

4. 按下 Calibration 按扭,做校準(zhǔn)工作,請(qǐng)參考下圖。

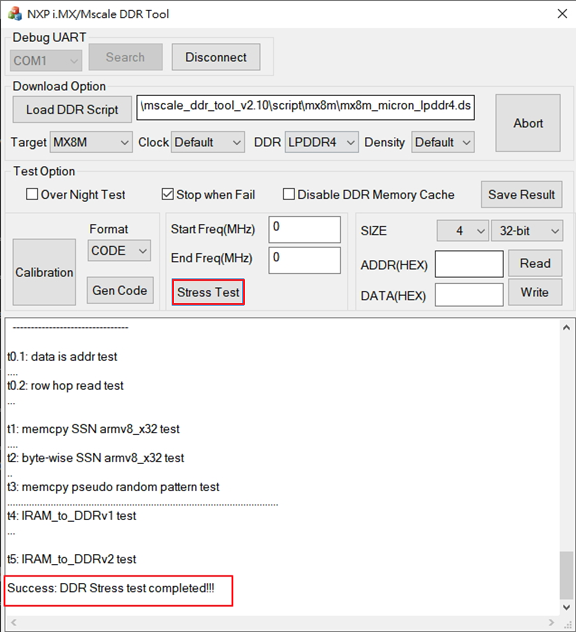

5. 按下 Stress Tess 按扭,請(qǐng)參考下圖。

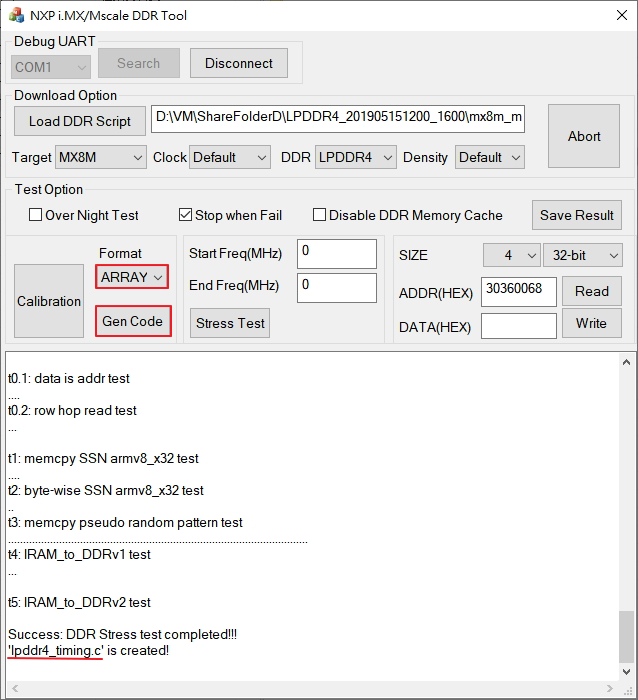

6. 使用的 BSP 版本為 L4.14.98_2.0.0_ga 版本,所以Format 選擇 "ARRAY" 格式輸出,然後按下 "Gen Code" 按扭,產(chǎn)生輸出檔案 lpddr4_timing.c,請(qǐng)參考下圖。

Chapter 5 DDR 參數(shù)整合 (Yocto)

5.1 BSP編譯流程

1. mscale_ddr_tool 參數(shù)整合至 BSP ---

放置 使用 3.4.2 步驟 (6) 產(chǎn)生的 lpddr4_timing.c 檔案,取代 "tmp/work/imx8mqevk-poky-linux/u-boot-imx/2018.03-r0/git/board/freescale/imx8mq_evk" 裡原生 lpddr4_timing.c 檔案。

2. Replace LPDDR4 Firmware (Optional) ---

使用 mscale_ddr_tool/bin 資料夾內(nèi) lpddr4_pmu_train_1d_imem.bin、lpddr4_pmu_train_2d_imem.bin、lpddr4_pmu_train_1d_dmem.bin、lpddr4_pmu_train_2d_dmem.bin 檔案,取代 "tmp/deploy/images/imx8mqevk/" 裡原生 lpddr4_pmu_train_1d_imem.bin、lpddr4_pmu_train_2d_imem.bin、lpddr4_pmu_train_1d_dmem.bin、lpddr4_pmu_train_2d_dmem.bin 檔案。

3. 產(chǎn)生imx-boot Image ---

在 Yocto 專案環(huán)境使用下列命令,產(chǎn)生 imx-boot image

$ bitbake u-boot-imx -c compile -f

$ bitbake u-boot-imx -c deploy -f

$ bitbake imx-boot -c compile -f

$ bitbake imx-boot -c deploy -f

輸出 Image (imx-boot-imx8mqevk-sd.bin) 在 "/tmp/deploy/images/imx8mqevk/" 資料夾

4. Flash imx-boot Image 到 SD 卡

$ sudo dd if=imx-boot-imx8mqevk-sd.bin of=/dev/sdx bs=1k seek=33

5.2 驗(yàn)證 DDR 參數(shù)

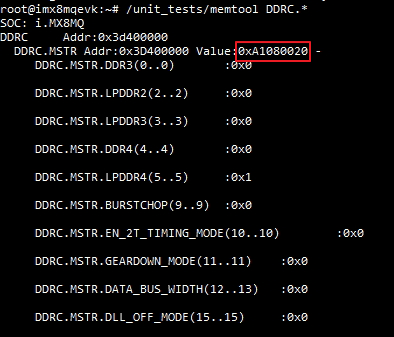

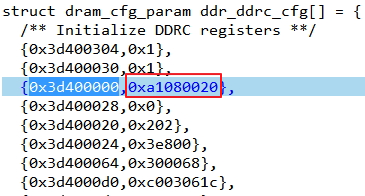

1. 使用 memtool 指令取得系統(tǒng)開機(jī)後 DDRC Register 值。

$ /unit_tests/memtool DDRC.*

2. 比對(duì) lpddr4_timing.c 檔案裡 DDRC參數(shù)是否正確寫入 DDRC (DDR Controller)。

Chapter 6 補(bǔ)充說(shuō)明

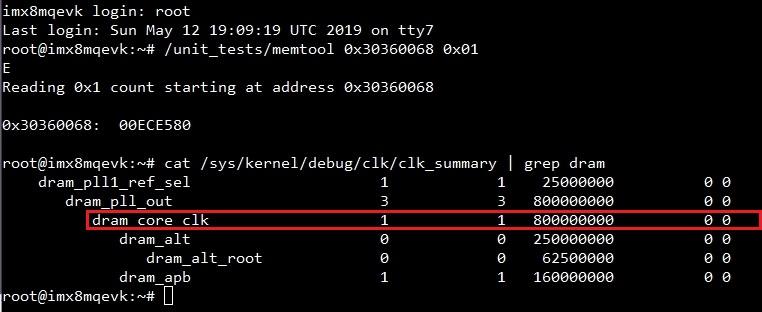

1. dram_core_clk、DRAM Clock、Data Rate 關(guān)係

(1) DRAM Clock = Dram_Core_Clk x 2

(2) Data Rate = DRAM Clock x 2 (Clock 正負(fù)緣取 Data)

實(shí)例:

$ cat sys/kernel/debug/clk/clk_summary | grep dram 得到 dram_core_clk 資訊,所以DRAM Clock 值為 1600MHz,Data Rate 值為 3200MHz。

下圖紅框得到 dram_core_clk 值為 800000000 Hz (800MHz)。

800MHz (dram_core_clk) x 2 = 1600MHz (DRAM Clock)

1600MHz (DRAM Clock) x 2 = 3200MHz (Data Rate)

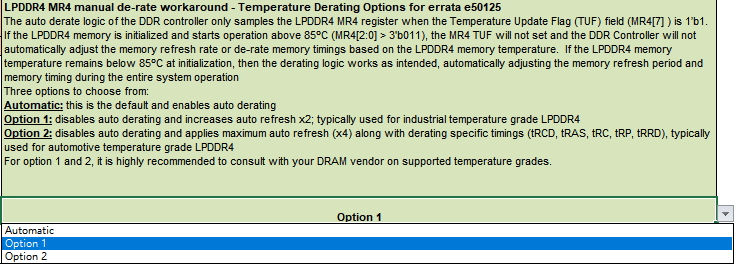

2. 專案開發(fā)必需確認(rèn)清楚 LPDDR4 晶片是屬於 Industrial 或 Automotive 規(guī)範(fàn),並填寫在 “LPDDR4 MR4 manual de-rate workaround” 欄位,因?yàn)槿菀自斐上到y(tǒng)運(yùn)行一段時(shí)間後當(dāng)機(jī),同時(shí)沒有任何 Log 訊息輸出。

Chapter 7 參考資料

1. MSCALE_DDR_Tool_User_Guide.pdf (Rev. V1.1.0)

2. 200b_z11m_ddp_pdp_auto_lpddr4_lpddr4x.pdf (Rev. C 12/17 EN)

[Micron LPDDR4 MT53D1024M32D4NQ-062 WT:B Datasheet]

參考來(lái)源