一.?前言

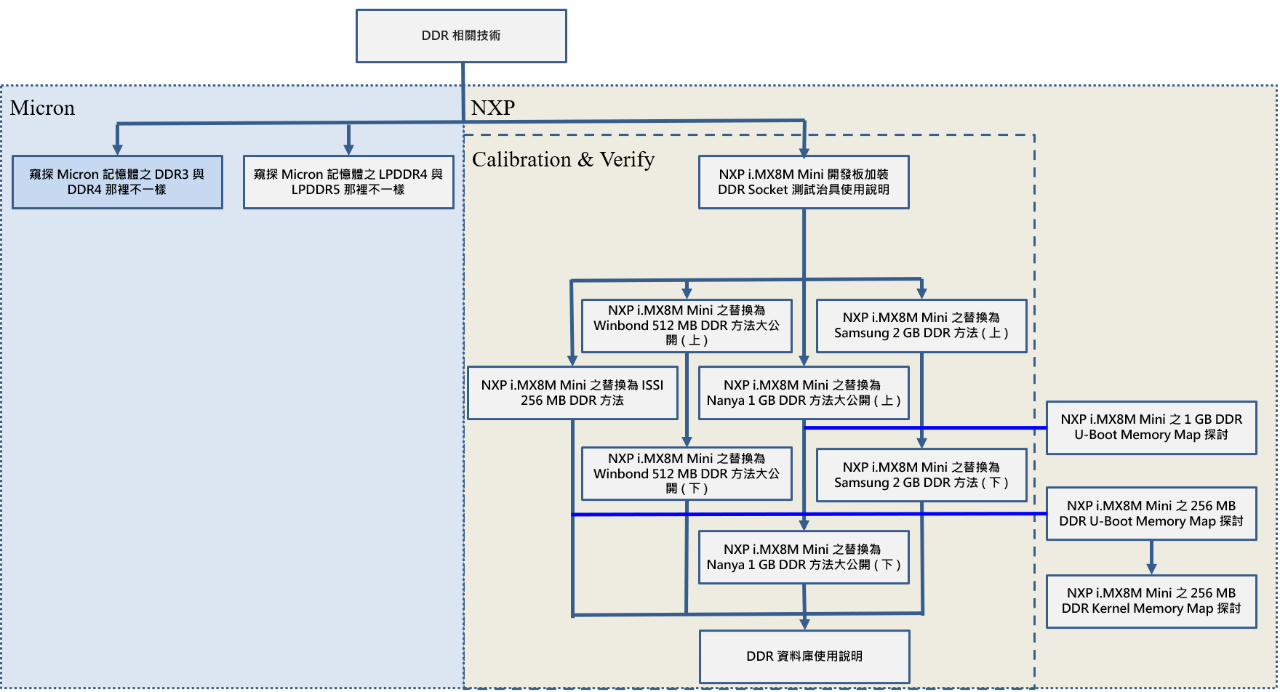

世平集團針對 DDR 相關技術整理了一系列博文,其中也包含了 Micron DDR 的相關技術。下圖為詳細的博文索引架構筆者希望能夠透過這些博文協助大家更了解 DDR 的相關技術,未來筆者也會持續更新此系列的相關博文還懇請支持!而本篇博文會針對 DDR 相關技術索引架構中的【ATU Book-Micron 系列-DDR】窺探 Micron 記憶體之 DDR3 與 DDR4 那裡不一樣?這篇文章做介紹。

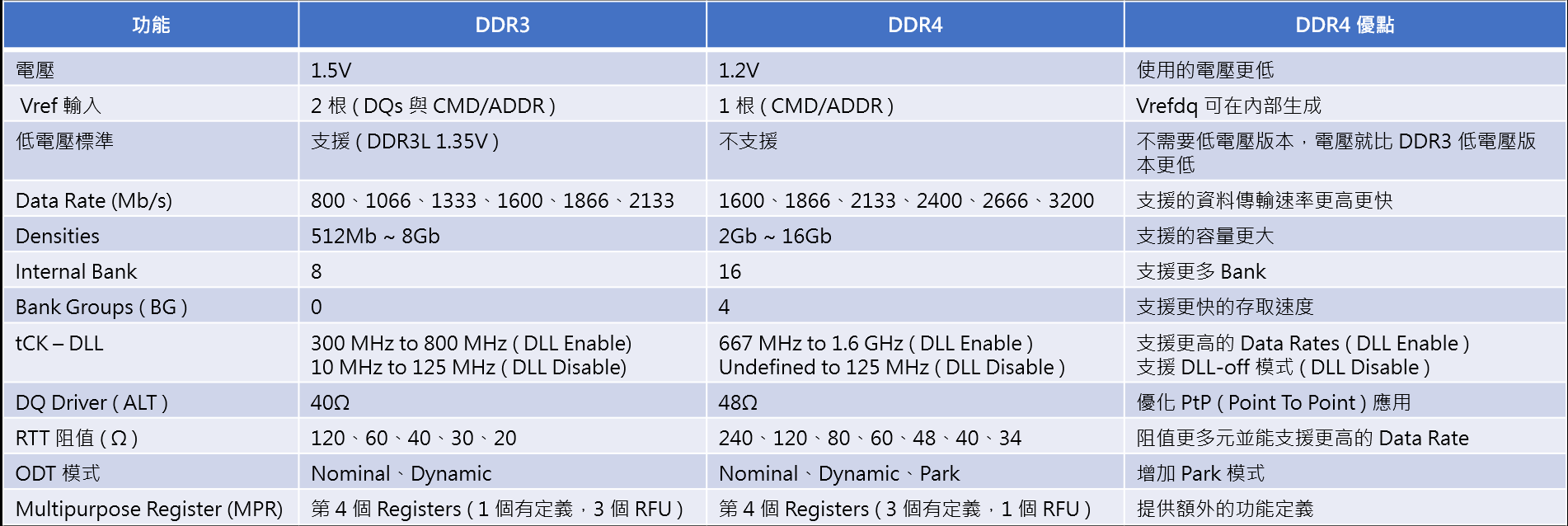

從各大報章雜誌甚至是科技新知網站 ( 例如 DIGITIMES ) 的文章中可以了解到 DDR4 是當前主流的記憶體。而 DDR4 比起 DDR3 有著更高的 Performance 和更強大的功能非常適合應用在 Micro-Server、Tablet 等領域上。

此外 DDR4 的好處有運行「電壓更低」以及「速度更快」等優勢。本篇文章將會整理出 Micron 的 DDR3 與 DDR4 不一樣的地方給各位讀者們參考,希望藉由此篇文章的分析讓各位讀者對 DDR4 更加了解。

以下筆者將會用 DDR4 的角度來與 DDR3 做比較。接著請各位讀者們繼續看下去吧!

?

二. DDR4 的電壓比 DDR3 的電壓更低

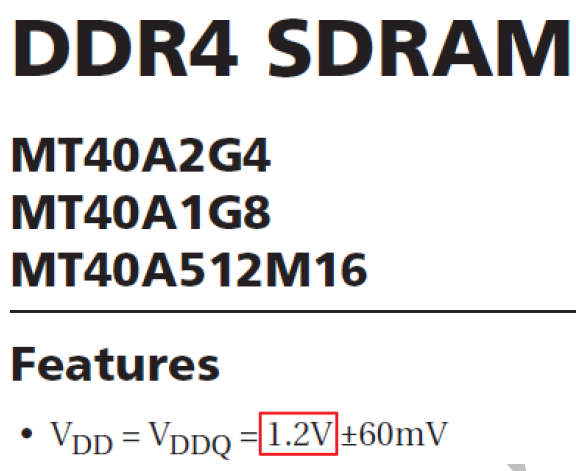

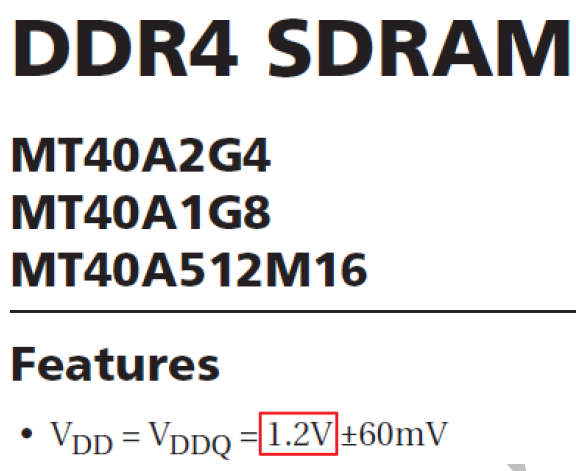

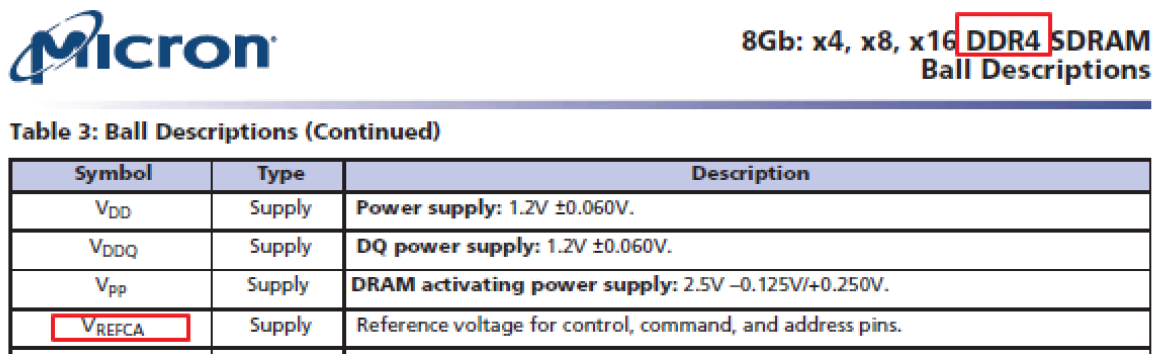

DDR4 VDD 的電壓降低為 1.2V ( 可參閱以下圖片 );DDR3 VDD 的電壓為 1.5V,相較之下 DDR4 明顯的更加省電了。

此圖來自 Micron DDR4 Datasheet。

?

三. DDR4 VREF Input Pin 的改變

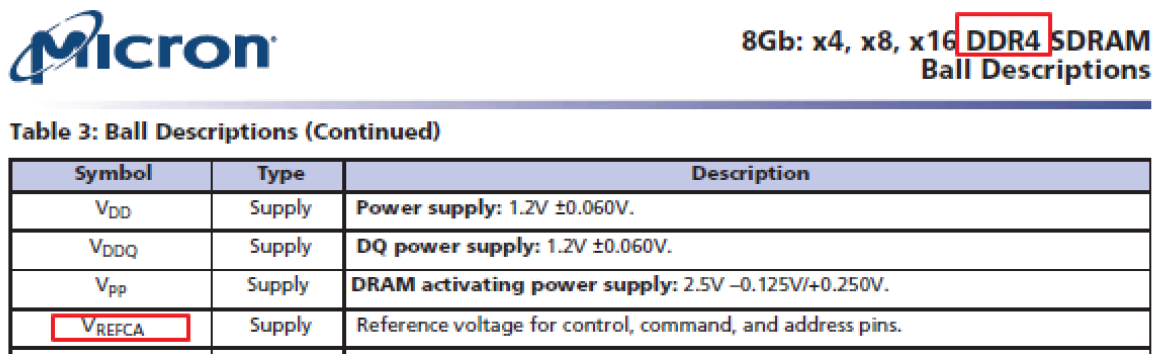

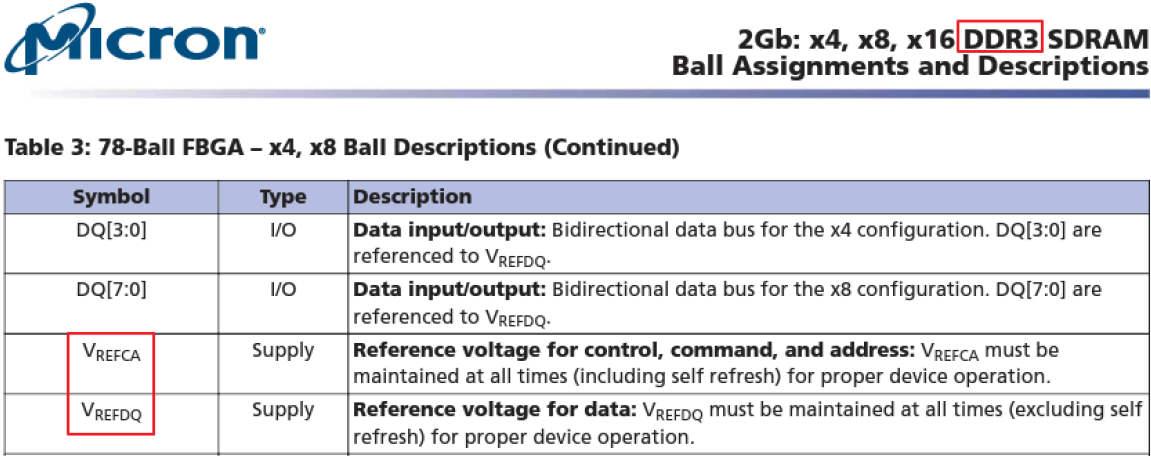

DDR4 的 VREF Pin 剩下 1 根 ( VREFCA );而 DDR3 的 VREF Pin 有 2 根 ( 分別為VREFDQ 與 VREFCA ) 我們可從 Datasheet 中看到差異 ( 也可參閱以下比較圖 )。

補充 1:VREF 就是參考電壓。筆者的理解為 VREFCA 就是 Command / Address Pin 的參考電壓;而 VREFDQ 就是 Data Pin 的參考電壓。

補充 2:DDR4 的 VREFDQ 是由內部生成。筆者的理解是可以透過修改 MR6[7]、MR6[6]、MR6[5:0] 等 Register 來做到開關或 Range 的調整 ( 詳細敘述可參閱 Datasheet )。

補充 3:MR 為 Mode Register 的簡寫。

此圖來自 Micron DDR4 Datasheet。

此圖來自 Micron DDR3 Datasheet。

四. DDR4 沒有低電壓版本

DDR4 工作電壓為 1.2V 並無其他低電壓的版本。在 DDR3 系列 DDR 中有一個低電壓的版本叫做 DDR3L;它的工作電壓可運作在 1.35V ( 一般標準的 DDR3 工作電壓是 1.5V ),值得一提的是 DDR4 的電壓 ( 1.2V ) 就比 DDR3L 的電壓 ( 1.35V ) 還低了。

?

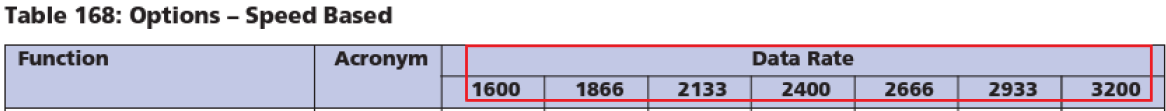

五. DDR4 的 Data Rate 更快

DDR4 Data Rate 傳輸速率範圍在 1600 MT/s 到 3200 MT/s 之間;而 DDR3 Data Rate 傳輸速率範圍在 800 MT/s 到 2133 MT/s 之間,比起 DDR3 的傳輸速度 DDR4 明顯快了很多 ( 多了 2400、2666、3200 等頻段 )。

補充 1:DDR4 比起 DDR3 多了 2400、2666、3200 等頻段。

補充 2:Data Rate 為 Clock 的 2 倍。舉例來說 Clock 如果是 1600 MHz 那 Data Rate 就是 3200 MT/s。

?

六. DDR4 Density 支援的容量更大

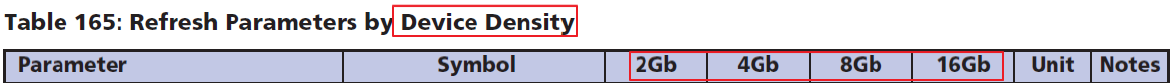

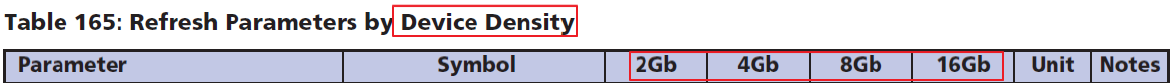

DDR4 Density 支援 2Gb ~ 16Gb,而 DDR3 Density 只支援 512Mb ~ 8Gb 明顯可以看到 DDR4 能支援的容量更大了。

可由下圖了解到 DDR4 支援的 Density 有哪些。( 此圖來自 Micron DDR4 Datasheet )

?

七. DDR4 支援更多 Bank

DDR4 與 DDR3 相比 DDR4 多了Bank Group 的這個概念,而每組 Bank Group 是由 4 個 Bank 所組成。從 Datasheet 中可以得知 x4/x8 Configuration 的 DRAM 有 4 組 Bank Group;而 x16 Configuration 的 DRAM 有 2 組 Bank Group。

值得一提的是 DDR4 Bank Group 的這個概念,可讓 Bank 對不同 Bank Group 的 Access 比在同一組 Bank Group 內的 Access 還快。( 詳細說明可參閱 Datasheet )

補充:將 Bank 拆分到 Bank Group 裡的好處,就是讓 DDR4 可以改善與提升 Bank Access 的時間。

從以上敘述可以得知 DDR4 最多可以支援到 4 組 Bank Group ( x4/x8 Configuration ),而一組 Bank Group 是由 4 個 Bank 組成。因此 DDR4 最多可以支援到 16 個 Bank,而 DDR3 最多只可以支援到 8 個 Bank。

下圖敘述了 DDR4 支援的 Bank 數量。( 此圖來自 Micron DDR4 Datasheet )

八. DDR4 DLL 頻率變高

DDR 的運作主要是依靠 Clock ( CK_t/CK_c ) 做為基礎來做到 Read / Write 等訊號的同步,而電壓或溫度的變化都可能會影響到 Clock 精準度進而導致 Read / Write 等的 Timming 出現問題。根據筆者的了解 DLL ( Delay Locked Loop ) 機制可以讓 Clock 的訊號同步問題得到改善在 DDR 技術裡是個相當重要的關鍵。由於 DDR4 的速度比 DDR3 更快的緣故因此 DLL 的速度也需要跟著增加。

值得一提的是 DLL 在 DDR 上電初始化階段會被 Enable ( 可參閱下圖 ),而主要是透過 MR1[0] 的Register 來做設置。而 DDR4 比起 DDR3 在 DLL Enable 時候有著更高的 Data Rate ( 667 MHz 到 1.6 GHz )。此外 DDR4 比 DDR3 更為彈性「多了 DLL-Off 模式可以使用」,而使用 DLL-Off 模式會影響到 Read Data 的部分訊號 ( 例如 tDQSCK )。

補充 1:根據筆者的理解當系統平臺想進入低功耗模式,可能會採取將 DDR 切換到 DLL-Off 模式的方式。

補充 2:關於 DLL Enable 與 DLL-Off 模式的更多敘述可參閱 Datasheet。

?

?

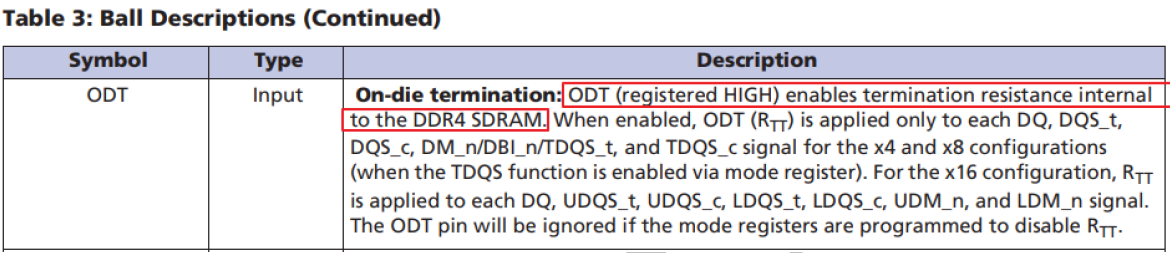

九. DDR4 ODT 的不同

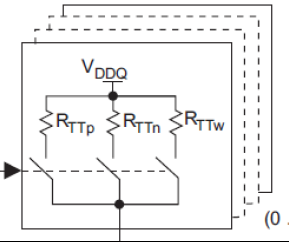

首先讓我們粗略的了解一下 ODT 是什麼,ODT 是 On-Die Termination 的縮寫。根據筆者的理解它指的是一根實體 Pin 腳也是一種訊號狀態的表示。一般常見訊號有 High Level 或 Low Level 這 2 種而 DDR 信號的傳輸非常快速所以對電路阻抗匹配的要求較高,因此多了 ODT 功能來做到對電阻值的細部調整進而達成讓訊號完整性更好之目的。

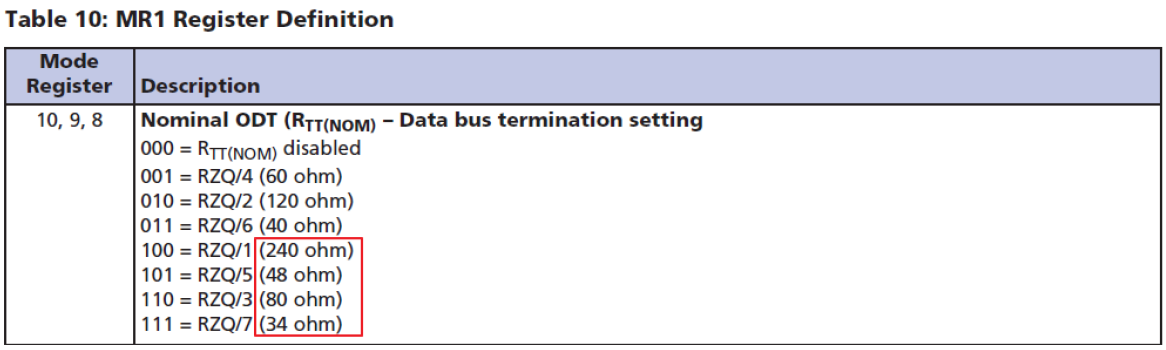

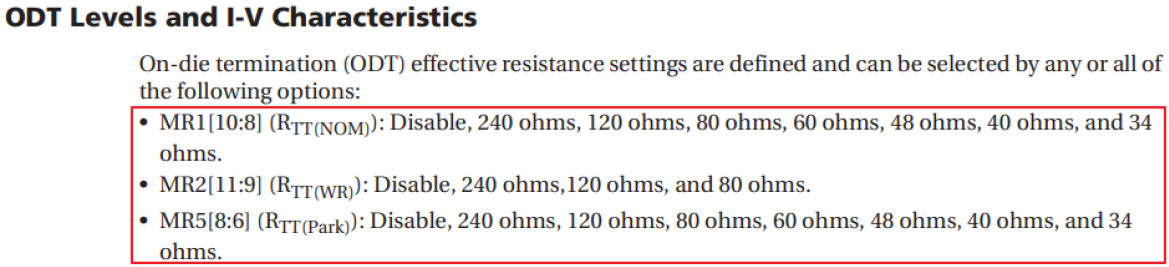

從 Datasheet 中可以得知設置 ODT Pin 腳為 High 以後透過改變 RTT 的電阻值可以改變 DQ、DQS_t/DQS_c 等訊號的強度。RTT 就是 DDR 裡面的終端電阻值可以透過 MR Register 做調整。

?

?

由於 DDR4 的信號傳輸比起 DDR3 的訊號更加高速所以對電路阻抗匹配的要求更高的關係,因此在 DDR4 增加了幾個電阻值 ( 分別為 240、80、48、34 Ohm;可參閱 DDR4 Datasheet MR1[10:8] Register ) 可以做到對終端電阻更加細微的調整。

?

值得一提的是 DDR4 還增加了新的 ODT ( On-Die Termination ) 模式 「Park」;稍早有提到開啟 ODT 功能後就可以設定 DDR 內部的終端電阻 RTT,因為 DDR4 的信號傳輸更加高速並且對電路阻抗匹配更加要求,所以可以透過修改 RTT 相關 Register 做到更加細微的終端電阻調整達到提升訊號的完整性的目的。

DDR4 的 ODT 模式共有以下 4 種狀態:

(1) Data Termination Disable。

(2)?RTT(NOM):就是 Nominal ODT ( RTT(NOM) ) 可修改 MR1[10:8] Register 來做電阻調整。

(3)?RTT(WR):就是 Dynamic ODT ( RTT(WR) ) 可修改 MR2[11:9] Register 來做電阻調整。

(4)?RTT(Park):就是 Parked ODT ( RTT(Park) ) 可修改 MR5[8:6] Register 來做電阻調整。

?

補充:根據筆者的理解「不同的 Case 對上述提到的 RTT(NOM)、RTT(WR)、RTT(Park) 的設置都會不同」。

先在這裡小結一下,由以上敘述可以得知 DDR4 比起 DDR3 的 RTT 多了一些電阻值可做到更加細微的調整,另外 DDR4 比起 DDR3 也多了一個 RTT(Park) 模式可以使用。DDR4 比起 DDR3 多了更多彈性的選擇可以讓信號的完整性更佳。

?

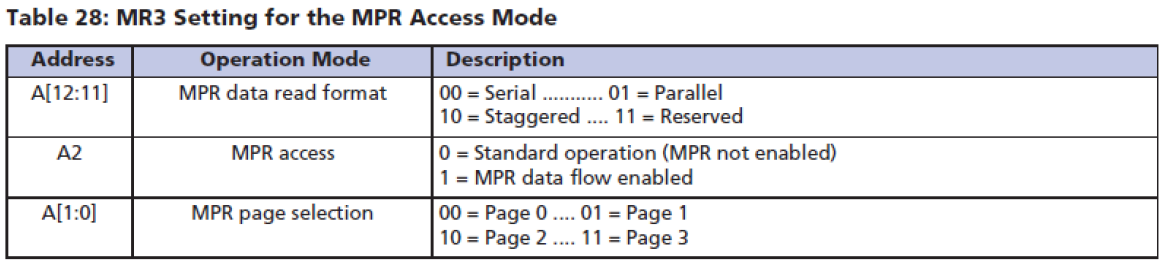

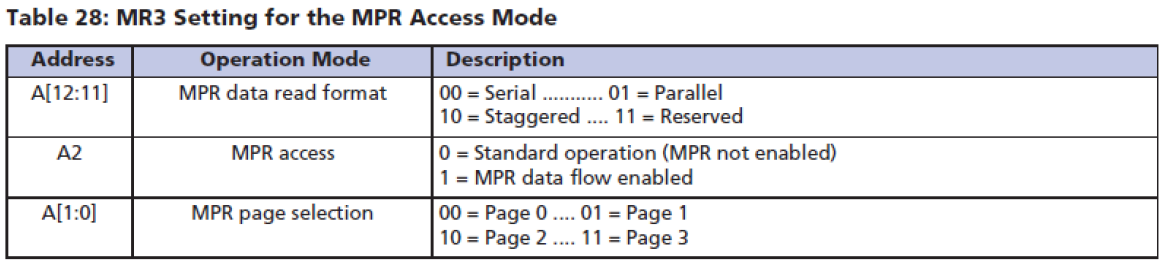

十. DDR4 MPR 增加新定義

DDR4 在 MPR ( Multipurpose Register ) 部分增加了新定義,添加了像是 MR3[12:11] ( MPR Data Read Format ) 之類的功能。在 DDR4 可透過操作 MR3[1:0]、MR3[2]、MR3[12:11] Register 來使用 MPR 功能。筆者的理解是:若將 MR3[2] 設置為 1 就是啟用 MPR 功能;而 MPR 啟用後將可以 Write / Read Specialized 的 Data 到 DRAM。

下圖為 DDR4 的 MPR 可以設置的模式。( 此圖來自 Micron DDR4 Datasheet )

十一. 結語

世平集團針對 DDR 相關技術整理了一系列博文,而本篇文章針對 Micron 的 DDR4 與 DDR3 不一樣的地方做了些粗略的介紹。DDR4 有 IO 電壓更低、運行速度更快、容量更大等優勢 ( DDR4 與 DDR3 詳細的不同處可參考以下的比較表 ),希望本篇文章的內容可以讓各位讀者對 Micron 的 DDR4 相關技術有更深入的體會,若未來讀者們有 DDR 的相關問題歡迎隨時與世平集團做討論,之後筆者也將會繼續產出與 DDR 有關的相關博文,請各位讀者拭目以待。

?

?

十二. 參考文件

[1] https://www.digitimes.com.tw/tech/dt/n/shwnws.asp?CnlID=1&id=628575&query=DRAM

[2]?https://www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr4/8gb_ddr4_sdram.pdf

[3]?https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr3/4gb_ddr3l.pdf?rev=8d4b345161424b60bbe4886434cbccf4

[4] https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/dram/ddr3/2gb_ddr3_sdram.pdf?rev=4bc67ac3a6f34250a2b73cb9db8c5502

[5]?https://blog.csdn.net/comeonbestxiaohe/article/details/84971448

[6]?https://www.computerdiy.com.tw/ddr4-ram/

[7] https://bbs.eetop.cn/thread-612579-1-1.html

[8]?https://blog.csdn.net/hierro_zs/article/details/54603417

[9]?https://community.nxp.com/t5/i-MX-Processors/i-MX-8M-Mini-configure-DLL-off-mode-using-LPDDR4-memory/m-p/1275517

[10]?https://blog.csdn.net/tbzj_2000/article/details/90762594

[11]?https://www.micron.com/products/dram/ddr3-to-ddr4

[12]?https://www.kingston.com/tw/memory/ddr4-overview

[13]?https://blog.csdn.net/hierro_zs/article/details/70238823

[14]?https://kknews.cc/zh-tw/news/j5jpbmy.html

[15]?https://www.micron.com/-/media/client/global/documents/products/technical-note/dram/tn0456_clock_jitter.pdf

[16]?https://kknews.cc/zh-tw/news/oxrl2yq.html

[17]?https://www.twblogs.net/a/5b80c55b2b71772165a93fc7

[18]?https://www.rambus.com/dllpll-on-a-dram/

參考來源